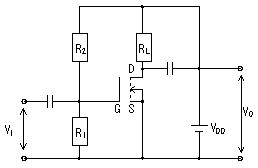

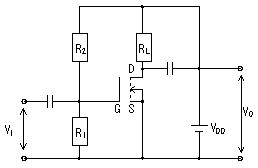

FETの増幅回路は下図のような回路です。

上図の回路で増幅動作点である、ゲート−ソース電圧VGS[V]は

![]()

となります。

FETの入力インピーダンスは、非常に小さいので、VGSは電源電圧VDDをR1とR2で分圧した値となります。

尚、上図の交流分等価回路は

となります。

Vo=RL・Id

Id=gm・vi

となります。

ただし、gmは相互コンダクタンスで

![]()

上式より、出力交流電圧Vo[V]は

Vo=RL・gm・vi

図1は、MOS形FET増幅回路を示し、図2は、そのFETの静特性を示す。ただし、R1=10[kΩ]、R2=20[kΩ]、RL=4[kΩ]、VDD=12[V]とするとき、次の(a)及び(b)に答えよ。

図1

図1

(a)ゲート・ソース間電圧VGSの値として、正しいのは次のうちどれか。

(1) 2 (2) 3 (3) 4 (4) 5 (5) 6

(b)入力交流電圧viの最大値が1[V]のときの出力交流電圧voを、図2の静特性曲線から求めた場合、voの最大値の値としていくらになるか。正しいのは次のうちどれか。

(1) 1 (2) 2 (3) 3 (4) 4 (5) 5

解説

ソース-ゲート間電圧VGS[V]は

![]()

VGSが5[V]のとき ID=2[mA]

VGSが3[V]のとき ID=1[mA]

相互コンダクタンスgm[S]は

![]()

出力交流電圧Vo[V]は

Vo=RL・gm・vi=4×103×0.5×10-3×1=2[V]

答え a-(3)、b-(2)

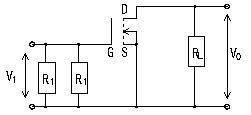

図のようなFET増幅回路がある。次の(a)及び(b)に答よ。

ただし、は抵抗RA、RB、RC、RD、REは抵抗、C1、C2、C3はコンデンサ、VDDは直流電源、IDはドレーン電流、v1、v2は交流電圧とす。

(a) 図の増幅器のトランジスタは、接合形の( ア )チャネルFETであり、結合コンデンサは、コンデンサ( イ )である。

また、抵抗( ウ )は、温度変化に対する安定性を高める役割を果たしている。

| ( ア ) | ( イ ) | ( ウ ) | |

| (1) |

|

|

|

| (2) |

|

|

|

| (3) |

|

|

|

| (4) |

|

|

|

| (5) |

|

|

|

(b) ドレーン電流ID=6[mA]、直流電圧源VDD=24[V]とし、ゲート・ソース間電圧VGS=-4[V]で動作させる場合、抵抗RA、RBの比RA/RBの値として、最も近いのはどれか。

ただし、抵抗RC=1.6[kΩ]とする。

(1) 1.2 (2) 1.9 (3) 2.4 (4) 3.8 (5) 4.7

解説

図のFETはnチャネルFETである。結合コンデンサは直流成分を抑圧するために取り付けられる。C1、C3が該当する。

安定出力を得るためには、入力バイアスを一定に保つようにRBに大きな電流を流す。

答え a-(1)、b−(2)